��ҳ��http://www.pttcn.net�������ּ�Ⱥ�Խ������ʧ��������о� ���߰������ּ�Ⱥ�Խ�����ʹ��ʱ������Գ������ʧ�����⣬����Խ����ڼ�Ⱥģʽ����ע����������ֱͨģʽ����ͨ�š�����ģʽ�²��ܽ���ָ����Ե����⣬���������������ָܻ��������һ���������Ϸ�����������ָ��ŵĿ������ź����������⡢����Ļ�·�˲����������⡢��Դ����������ȡ���Կ��ܵ�ԭ����������Ͳ��ԣ��ó������Դ���˲����ݡ���ͬʱ���ӻ�������·����������������״̬�Ľ����������ʾ�������Խ���������Կ���������������շ��л�ʱ��ѹ������ɵ����ʧ�����⣬�Խ������ȶ��ɿ��Եõ������Ը��ơ�

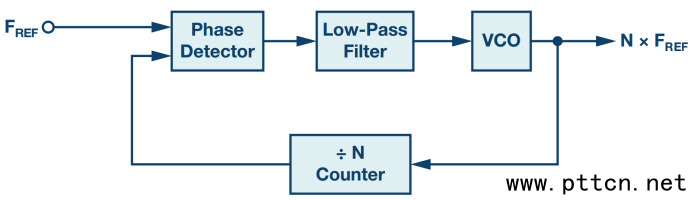

������Ŀ��2023���ʵǼƻ����������ܴ����������ǻ�У���ܼ��ŵ�ϵͳ�о�����Ŀ���pdjh2023 b1117 ����㷺Ӧ����Ƶ�ʺϳɡ�ʱ�ӷ��䡢��λ����Լ�ʱ�ӻָ��ȣ�������ͨ�š�������·����Ƶ�շ������ͼ�����ȱز����ٵ�һ���֣����ȶ��Զ���ȷ����������ϵͳ�����ܾ�����Ҫ����[1-2]�����ּ�Ⱥ�Խ����ڳ��»�����25�棩ʹ��ʱ����������ʧ���������¶Խ����ڼ�Ⱥģʽ����ע����������ֱͨģʽ����ͨ�š�����ģʽ�²��ܽ���ָ����Ե����⣬�ڵ��»����£�-40�棩����ָ��ʱ���ʧ�����ֵĸ��ʸ�����ͨ��������ʧ����ԭ�������ʵ�������ó�������ʧ������Ľ���������������Դ���˲����ݡ���ͬʱ���ӻ�������·����������������״̬�� 1 �Խ����������ԭ�� �����PLL����·�����ڸ��ָ�ƵӦ���У��Ӽ�ʱ�Ӿ�����·�����������ߵ�ͨ����·�ı���LO���ȡ������һ��ʵ����λ�Զ������Ŀ���ϵͳ������������ǽ��ο��źŵ���λ��ɵ������źŵ���λ���бȽϣ����ȽϽ��������̬�������Ƶ�ʺ���λ�������������Ƶ�ʺ���λƥ��ʱ�������������[3-4]�� ���ͨ���ɼ�Ƶ��������PD������·�˲�����LPF����ѹ������(VCO) 3 �������[4]���������ɿ�ͼ��ͼ1 ��ʾ����Ƶ������������ο�Ƶ��FREF����λ�뷴���źŵ�Ƶ�ʺ���λ���бȽϣ����ݱȽϽ������õ���IC������·�˲������ֺ��γ�ѹ������VCO�ĵ�г��ѹUCȥ����VCO��Ƶ�ʺ���λ��ʹ֮������������������ͬƵ�ʼ���λ��

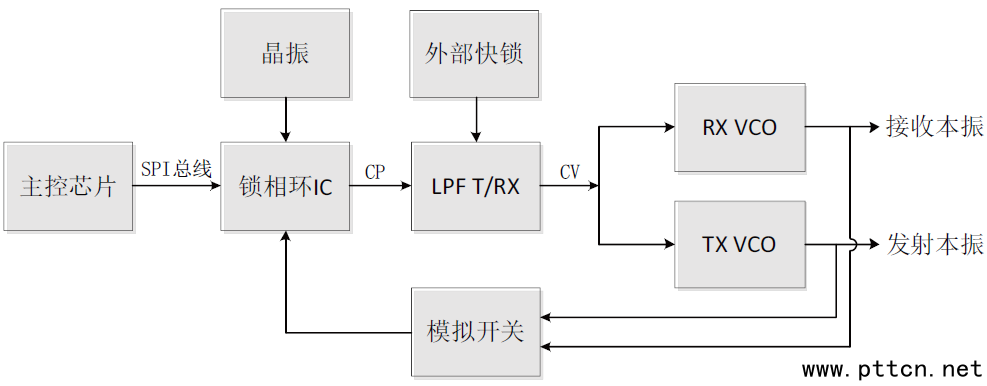

ͼ1 �����ɿ�ͼ �Խ����Ĺ���Ƶ����300 MHz �� 400 MHz ֮�䣬����С����Ƶ�������ƿ�ͼ��ͼ2 ��ʾ���乤��ԭ��Ϊ������оƬ����ʱ��Ҫ��ͨ��SPI �������������Ƶ����Ϣ��ͬʱ����ģ��ء�ѡ��·�˲����Լ������ⲿ����ģ�飬ʹVCO ������������Ƶ�㡣

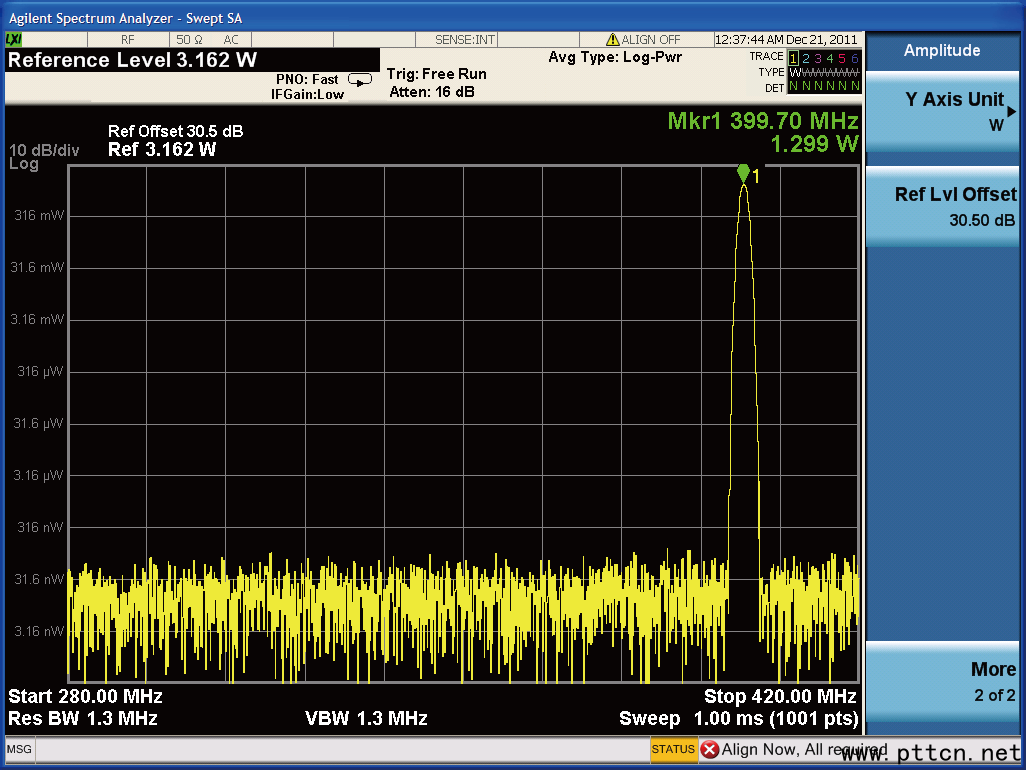

ͼ2 �Խ������ԭ����ͼ 2 ������ʧ����ԭ����� ����1�����»����£��Խ�������ʹ�ù����У���κ��к���ֺ���ʧ�ܡ��ͱ���������������ʧ�ܵ�����������ָ��ʲ��ߣ������ָ������ͨ�����߿ڲ��Թ��ϻ����ķ���ָ�꣬���������л����ĸ�Ƶ�㣺 1���Խ��������Ƶ�㶼��399.70 MHz ��������ͼ3��ʾ��

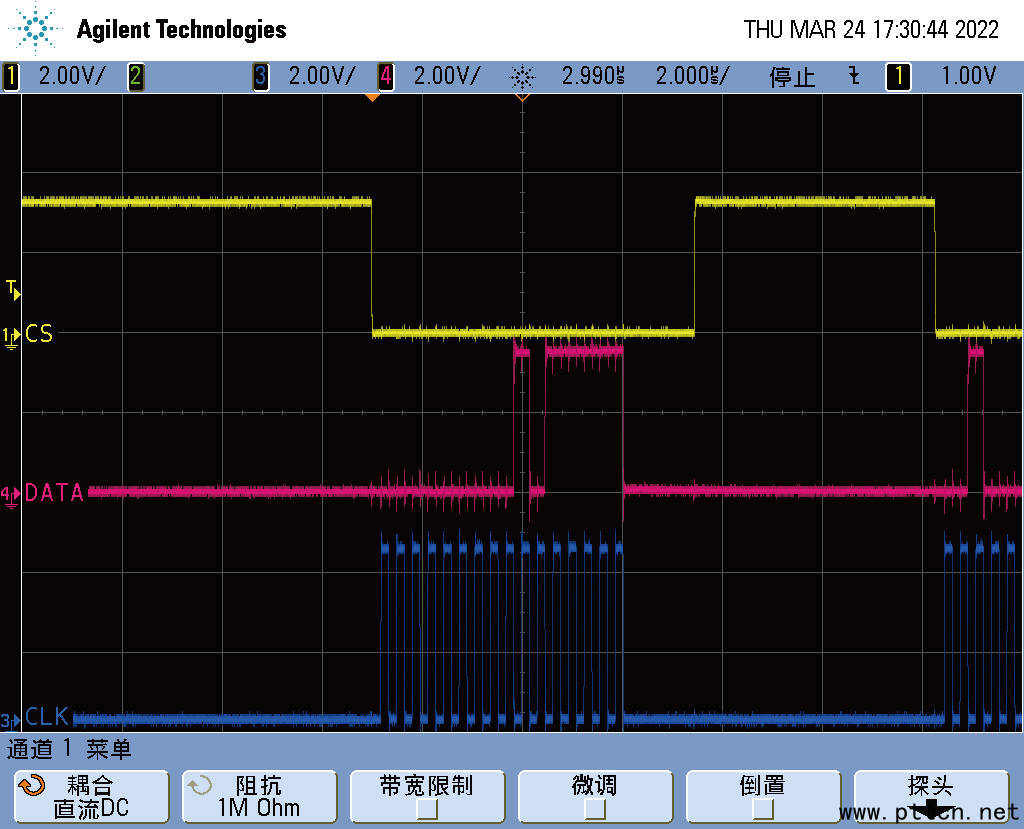

ͼ3 ���ʧ������ 2����ʾ�������������·�˲����������ѹCV��Ҳһֱ���ֲ��䣬��������²�ͬƵ��CV ֵ��ͬ���ݴ˿����жϹ��ϻ��������ʧ���ˡ� ����2�����»����£�-40�棩�����ԶԽ����ķ���ͽ�������ָ��ʱ�����һ��ʼ�Ͳ��Է���ָ�꣬�Խ�����������������һ���л����������ܲ��ԣ��ͳ������ʧ�������һ��ʼ�Ͳ��Խ���ָ�꣬�л�������ָ�����ʱ���Խ���Ҳ�����������������л��ؽ���ָ����ԣ��ͻ�������ʧ����������2̨����100% ���ָ������ҳ��ֺ������л����ĸ�Ƶ�㣬Ƶ���Dz��Ե�Ƶ�㶼��399.70 MHz��CV ֵҲ���ֲ��䡣��������������������Եó��������ۣ� 1���������ʧ�������ڶԽ����ɡ����䡱�л��������ա�״̬ʱ���ֵģ� 2�����º͵��»����³������ʧ������ԭ����һ�µģ����»����������������Բ��������ֵĸ��ʲŸ��ߣ� 3�����ݾ��飬�������ź�����������·�˲����������û���Դ���������¡� 4����Կ��ܵ�ԭ������������������ԣ��Ӷ��ҵ�����ĸ���ԭ�������������� 2.1 �ź������� ����оƬͨ��SPI ���߶����IC����Ƶ���������������ã����IC �ٸ��ݲ�ͬ��Ƶ�������ͬ��CVֵ��Ϊ���˳�SPI �����ϵĸ��š�ë�̣�������SPI ���ߵ�ʱ�ӣ�CLK�������ݣ�DATA����Ƭѡ��CS�����ϴ�����22 �� ���裬�Եز�����33 pF ���ݣ���˳�����Ϊ��SPI ����Ƶ�ʸߡ��ź����������ѣ�����֮��ͨ���쳣����������ʧ�ܲ����ʧ���� ��ʾ��������SPI ���ߵIJ�����ͼ4 ��ʾ���Ӳ��η�����SPI �����ź������пɣ�����������ʧ������SPI �����Ͻӵĵ��ݶ�ȥ��������ij�0 �����Խ�����Ȼ��ʧ��������ų�SPI �����ź������Ե�ԭ��

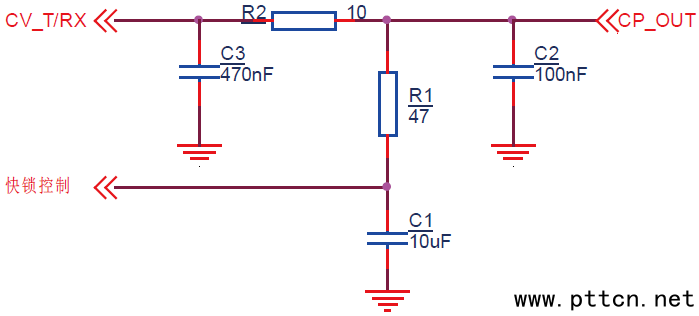

ͼ4 SPI���߲��η��� 2.2 ��·�˲������� ���ʧ�����л�Ƶ��ʱ��VCO�����Ƶ�ʺ�VCO�ĵ�г��ѹCV_T/RX�����ֲ��䣬���Ҳ�п����ǻ�·�˲����IJ�����������£�������·�˲����Ŀ������Ƶ�·�� �ѿ������Ƶ�·�Ͽ����������·�˲���·��C1ֵ���ڵ��»����½��в��ԣ�������ɻ�ʧ�������Ҳ����ȷ�ϲ��ǻ�·�˲���·�����⡣

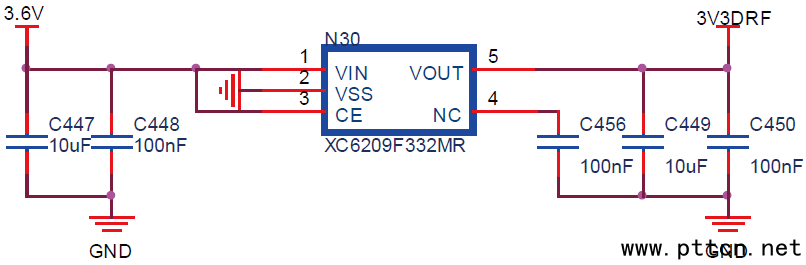

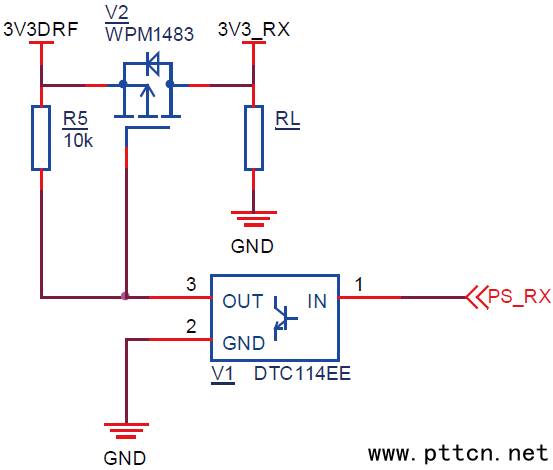

ͼ5 ��·�˲�����· 2.3 ��Դ������ ǰ���ᵽ�����ʧ�����ڶԽ����ɡ����䡱�л��������ա�ʱ���ֵģ������������������ɡ�����ת���ա��Ĺ����У������������¶����� 1�������������IC ��Ƶ����Ϣ�� 2���رշ�����·�ĵ�Դ�� 3��������·�ĵ�Դ�� �����ʧ����SPI ���ߵIJ���ʱ�����������ȷ������оƬ����������������Ϣ����˲��ų����շ��л������е�Դ�Ĵ��ر���ɵ�ѹ�������������ʧ���� ������·�ĵ�Դ��·��ͼ6��ʾ�����У� ��Դ3V3DRFͨ��MOS ���ر��3V3_RX����������·���硣ͬʱ��3V3DRF �������оƬ����Ƶ���ֻ�оƬ�ȹ��硣

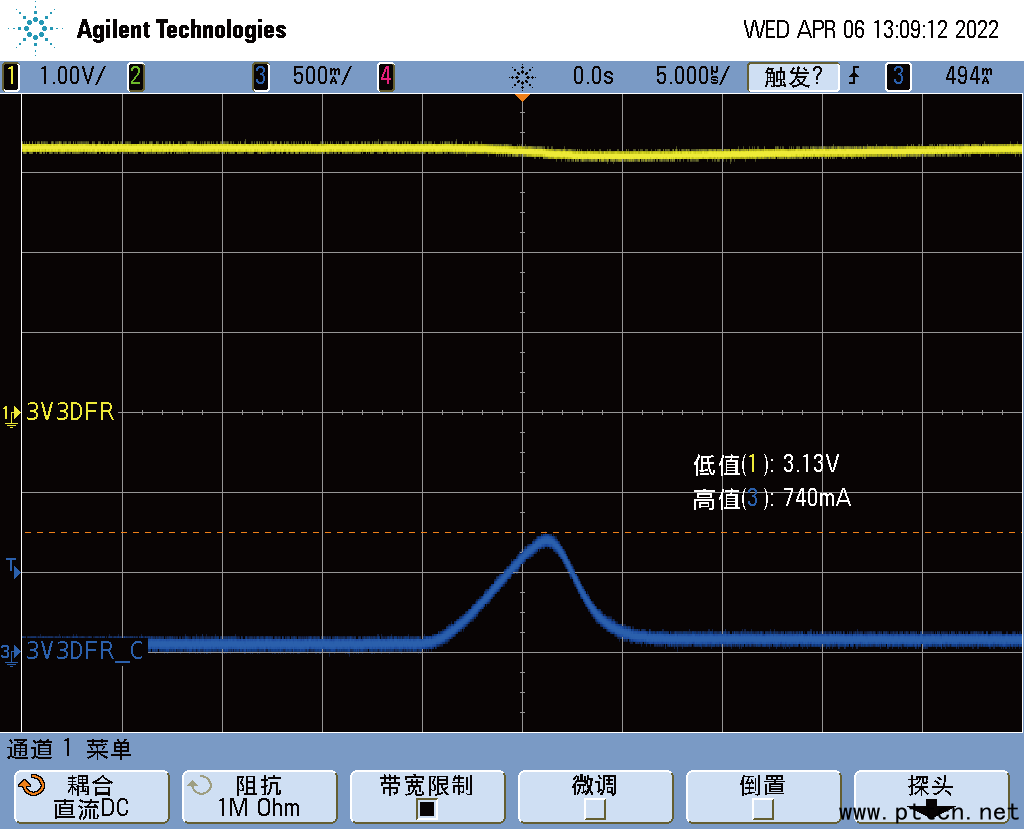

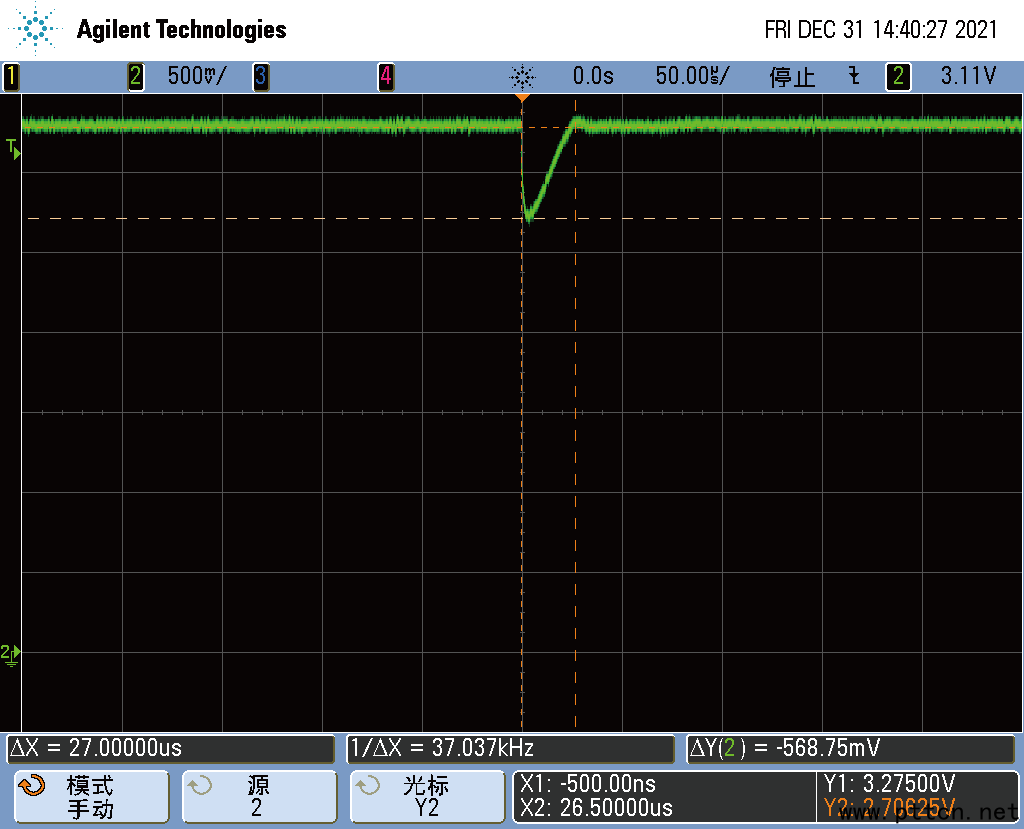

ͼ6 ������·��Դ���� ��ʾ��������3V3DRF��3V3_RX �IJ��Σ��ڶԽ����ɡ����䡱�л��������ա�˲�䣬����3V3DRF ��3.3 V ���䵽2.7 V��������3.3 V����ͼ7 ��ʾ�� ����������Խ���������������·����� 1������3V3DRF Ҳ�����оƬ���磬�������ʾ���оƬ�ܽ��ܵ���͵�Դ��ѹ��2.7 V������2.7 V��������оƬ���縴λ�� 2������оƬֻ�ڶԽ�������ʱ�ų�ʼ�����оƬ��ʹ�ù����У����оƬ�͵縴λ������оƬû�ж����ʼ�����ã����оƬ�ڲ��Ĵ������븴λ���Ĭ��״̬����������оƬ���ơ������Ϊʲô���ʧ���Խ��������Ƶ��ͻ�·�˲����������ѹCV ������Ƶ���л����仯�����������Խ����ſ��ԡ� 3��ͬʱ�����»��������оƬ���ܱ��ܽ��ܵ���͵�ѹ����2.7 V�����Ե��»��������ʧ�����ֵĸ��ʱȳ���ʱ���ߡ�

ͼ7 ��Դ3V3DRF���� 3 ʵ��������� ��Ե�ѹ����������ʧ�������⣬����Ҫ�ҵ���ɵ�ѹ����ĸ���ԭ���ܴӸ����Ͻ�����⡣���ڽ���ͨ·�ϵ��˲������������Ŵ��·����Ƶ������Ƶ�Ŵ��·��ģ�鶼����3V3_RX ���磬���Ĵ��������ϵ�˲�䣬���ܳ���˲ʱ�������ɵ�ѹ���䡣Ϊ�����Dz�����3V3DRF ����˲�䣬��3V3DRF ����3V3_RX�ĵ�������ͼ8 ��ʾ��

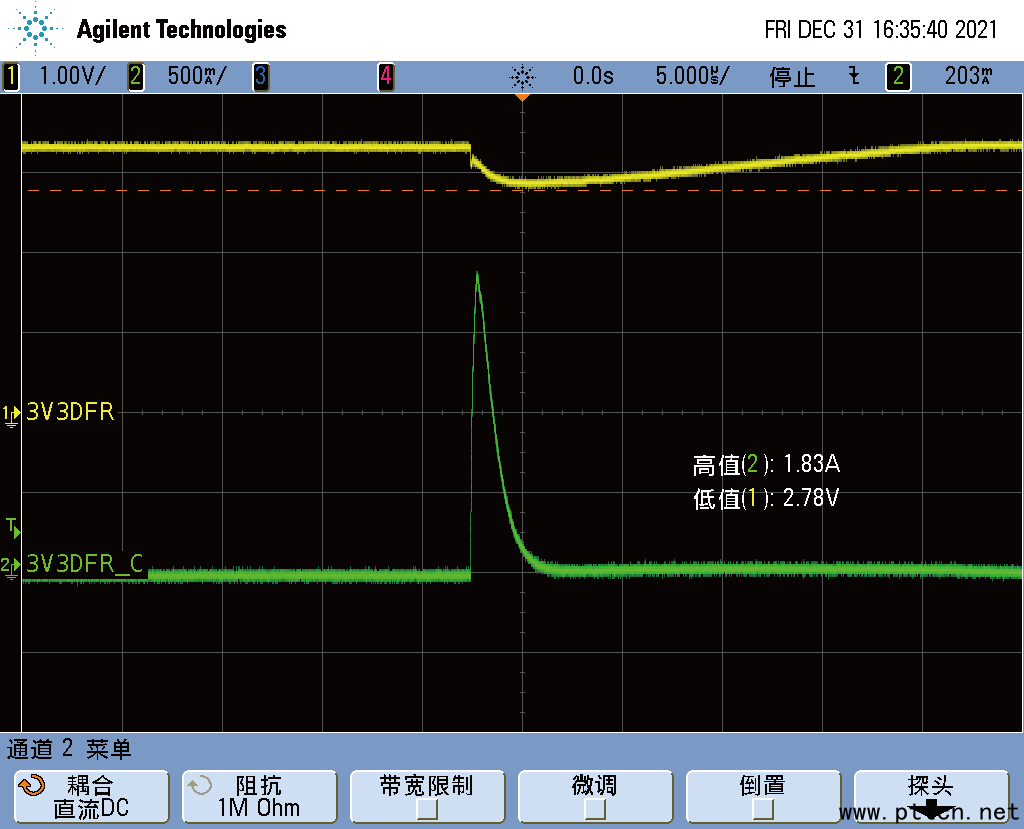

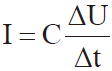

ͼ8 ��Դ3V3DRF��ѹ�͵���ͻ�� �Ӳ��Խ���������Խ����ɡ����䡱�л��������ա�˲�䣬����ͨ·3V3_RX �������˸ߴ�1.83 A ��˲̬���������3.6 V ת3V3DRF ��LDO(XC6209F332) ����������ֻ��0.5 A�����������������3V3DRF ��ѹ������2.78 V�����յ��������ʧ���� ����ԭ����������������µĽ�������� 3.1 �����Դ���˲����� �Ӵ�LDO���˲����ݣ���ͼ9 ��ʾ��LDO�����������ֻ��0.5 A��3V3DRF ���˲�����ֻ��10 ��F�������ص��������ϴ�ʱ��LDO ���˲����ݴ����������㣬��Ȼ���ֵ�ѹ�����������ڵ�ǰ���������Ҳ���������������LDO�����������˲�����C449 ��������˲�������C449 �ṩ������ֵ����ʽ��1�����㣺

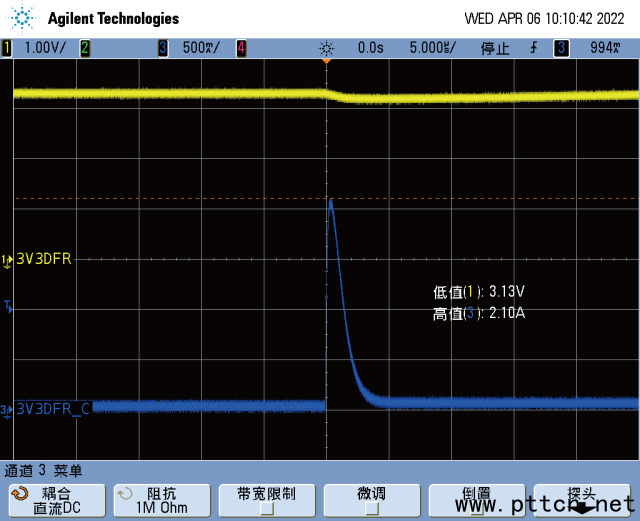

��֪˲ʱ�����I ��1.83A��ʱ�䦤t ��2.5 ��s������Ҫʹ��ѹ�������С��0.1 V����ô����C449 ����С��45.75 ��F����������װ����ѹ�����ƣ�C449 ����47 ��F�� ��C449 �ij�47 ��F �Խ����ӡ����䡱�л��������ա�ʱ����Դ3V3DRF�IJ��α仯��˲ʱ������ͼ9��ʾ���Ӳ��Բ��η�����C449 ��ֵ�����3V3DRF ��ѹ��������õ������Ը��ƣ���������ֵ��֮ǰ��2.7 V������3.13 V���������оƬ�Ĺ����������շ��л�˲�����û�б䣬���ɴ�������˲��������µ�ѹ���䣬�������ʧ���Ŀ����ԡ�

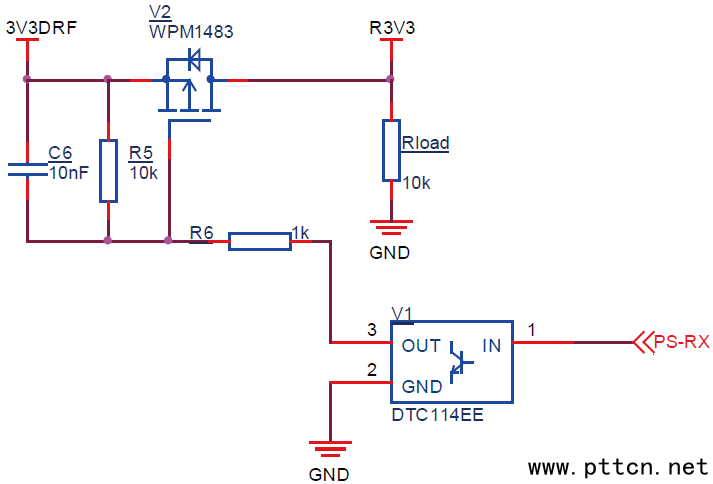

ͼ9 �ĵ��ݺ��ѹ������� �Ӳ��Բ��η�����C449 ��ֵ�����3V3DRF ��ѹ��������õ������Ը��ƣ���������ֵ��֮ǰ��2.7 V������3.13 V���������оƬ�Ĺ����������շ��л�˲�����û�б䣬���ɴ�������˲��������µ�ѹ���䣬�������ʧ���Ŀ����ԡ� 3.2 ���ӻ�������· ��С�շ��л�ʱ3V3_RX �ϵ�˲��ĵ�����MOS�ܵĵ�ͨ������VGS �仯���仯����ͼ10��ʾ��

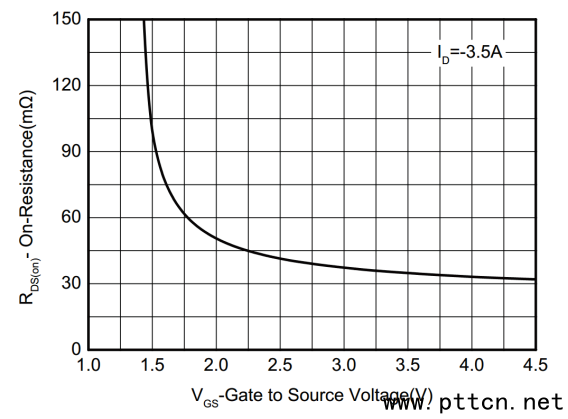

ͼ10 On-Resistance vs. Gate-to-Source voltage��ͨ������դ��-Դ����ѹ ��ͼ11 ��ʾ����MOS ���ص�·������C6��R6�����ɻ�������·����MOS �ܵ�ͨ˲�䣬����C6 ͨ������R6 �����ŵ磬ʹVGS �������ߣ�MOS �ܵ�ͨ���軺����С���ڵ�ͨǰ�����������ã��ﵽ��С˲ʱ������Ŀ�ġ�������ʱ�䣨MOS�ܵ�ͨʱ�䣩�ɰ�ʽ��2�����㣺 ��=R��C (2) ���뻺������·��MOS�ܵ�ͨʱ���ӳ�����Ӧ�ģ�MOS�ܵĽ�ֹʱ��Ҳ�ӳ��ˡ��ر�MOS ��ʱ�����ڵ���C6���˵�ѹ����ͻ�䣬��Դ3V3DRF ͨ��R5 ��C6��磬��VGS �� VGS��TH��ʱ��MOS �ܲų���ֹ�����ʱ�������������ʽ���㡣 �Խ����ӷ����л�������״̬ʱ��˲����������ʱ��2.5 ��s��������ʱ��Ӧ����2.5 ��s�����ڶԽ����շ��л�ʱ϶��1 ms�����MOS �ܵĵ�ͨ�ͽ�ֹʱ�䲻�ܴ���1 ms���������㼰ʵ����֤��R5��R6��C6 ����ͼ11 ��ʾ������MOS �ܵ�ͨʱ��Լ10 ��s��MOS �ܹر�ʱ��Լ100 ��s��

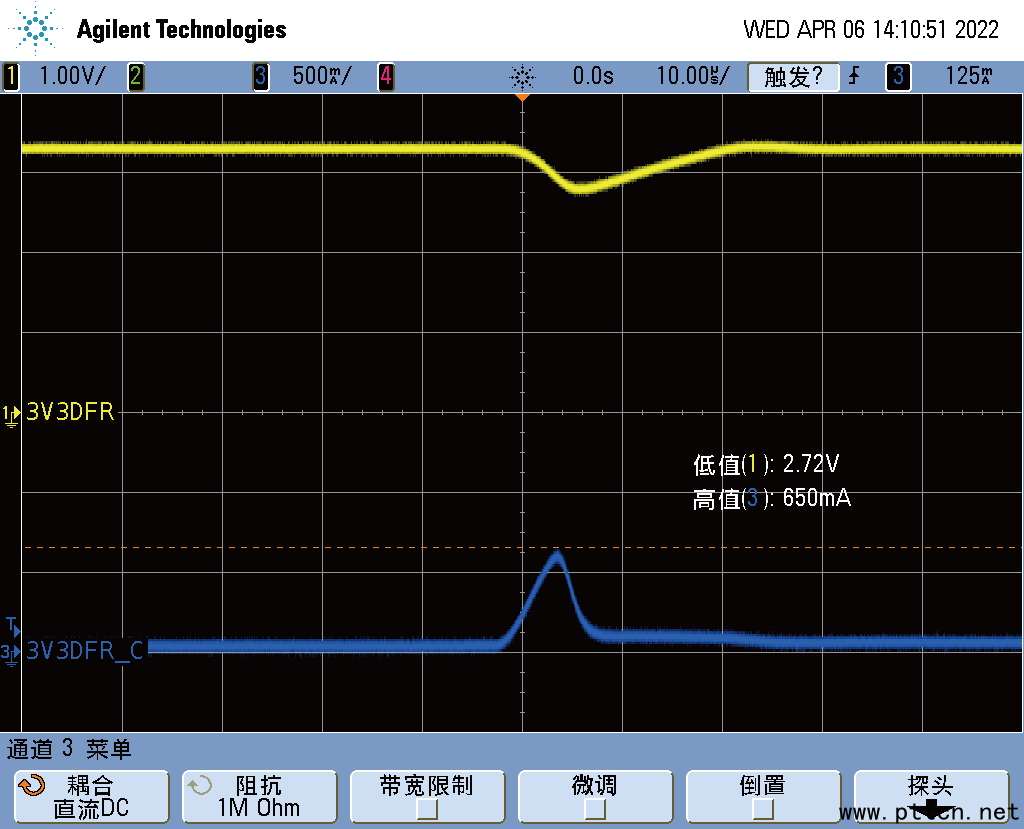

ͼ11 ��������· ���ӻ�������·R6��C6���Խ����ӡ����䡱�л��������ա�ʱ����Դ3V3DRF �IJ��α仯��˲ʱ������ͼ12 ��ʾ�� ��ͼ12 ���η��������ϻ��������շ��л�˲�������2.1 A ������0.65 A����Ȼ˲��������Լ�С��������LDO ��������������0.65 A�����Ե�ѹ������2.72 V�������Ȼ�����ʧ������

ͼ12 �ӻ��������ѹ������� Ҫ�볹������ʧ�������⣬��Ҫ˫�����£���C449 �ij�47 ��F��ͬʱ���ϻ�������·�����Բ�����ͼ13 ��ʾ��

ͼ13 �ĵ��ݼ��ӻ��������ѹ������� ����C449 ����ֵ�����ϻ�������·��˲��������͵�0.74 A����Դ3V3DRF ����3.13 V������������оƬ�͵縴λ������β��ԣ��������ڳ��»��ǵ��»����£���û�г������ʧ��������������оƬʵʱ������оƬ����״̬��������ȶ��Խ�һ���õ����ϡ� 3.3 ʵʱ������оƬ״̬ ����оƬʵʱ������оƬ״̬�����оƬ��һ���������ţ������оƬʧ��ʱ������������͵�ƽ��������оƬ�����ʧ���������³�ʼ��оƬ�������оƬ�ָ������� 4 ������ �������ش����۳����������������ʧ�������⣬ͨ���ų������Կ��ܵ�ԭ����ж�β��Զ�λ�����յó������Դ���˲����ݣ��Լ����ӻ�������·����������������״̬�Ľ������������������շ��л�ʱ��ѹ������ɵ����ʧ�����⣬�Խ������ȶ��ɿ��Եõ������Ը��ơ� �ο����ף� [1] �x����. �����·�Ŀɲ�������о�[D].�Ͼ�:���ϴ�ѧ,2018. [2] ���Ļ�.һ�ָĽ��͵Ŀ����������[J].������Ϣ�Կ�����,2020,35(3):91-94. [3] �Ӫ,�Ż���,����,��.�����������У������������ʵ��[J].��������,2021(8):113-116. [4] ������,�;���,�����.��Դ�����˲�������Ľ����[J].��������Ч��������,2020(8):84-87+99. [5] ������,������,ѦС��.һ�ַ�ֹ�������ӳ�������������[J].�й����ɵ�·,2021,30(12):39-41. [6] ����,������,����,��.һ�ֿ��������������·�ṹ���о�[J].���ɵ�·Ӧ��,2021,38(8):10-11. [7] ����,������,��ά��,��.���ڸĽ��ͻ�·�˲����ĵ������[J].����ϵͳ���������,2021,49(13):135-141. [8] ����ɽ,������,��Ӣ��,��.г���Ը�ѹֱ�����ϵͳ����վ�������Ӱ��[J].�㶫����,2020,33(11):91-101. [9] ����Ӣ,��۱�.������Ʒ������Ż���������[J].���Ӳ���,2020(20):45-46+25. [10] �ܹ���,���,���ӷ�.��������Ӧ��·�˲��㷨��ȫ���������������[J].����ѧ������,2020,37(9):62-67+72. ��������Դ�ڡ����Ӳ�Ʒ���硷��־2023��7���ڣ� (�й���Ⱥͨ���� | ���α༭�����) |

(1)

(1)