жївГЃЈhttp://www.pttcn.netЃЉЃКЛљгкDSPКЭSOPCЪ§зжаХКХЗЂЩњЦїЕФЩшМЦ

O в§ бд

Ъ§зжаХКХЗЂЩњЦїЪЧдкЕчзгЕчТЗЩшМЦЁЂздЖЏПижЦЯЕЭГКЭвЧБэВтСПаЃе§ЕїЪджагІгУКмЖрЕФвЛжжаХКХЗЂЩњзАжУКЭаХКХдДЁЃЖје§ЯваХКХЪЧвЛжжЦЕТЪГЩЗжзюЮЊЕЅвЛЕФГЃМћаХКХдДЃЌШЮКЮИДдгаХКХ(Р§ШчЩљвєаХКХ)ЖМПЩвдЭЈЙ§ИЕРявЖБфЛЛЗжНтЮЊаэЖрЦЕТЪВЛЭЌЁЂЗљЖШВЛЕШЕФе§ЯваХКХЕФЕўМгЃЌЙуЗКЕигІгУдкЕчзгММЪѕЪдбщЁЂздЖЏПижЦЯЕЭГКЭЭЈаХЁЂвЧЦївЧБэЁЂПижЦЕШСьгђЕФаХКХДІРэЯЕЭГжаМАЦфЫћЛњаЕЁЂЕчЩљЁЂЫЎЩљМАЩњЮяЕШПЦбаСьгђЁЃ ФПЧАЃЌГЃгУЕФаХКХЗЂЩњЦїОјДѓВПЗжгЩФЃФтЕчТЗЛђЪ§зжЕчТЗЙЙГЩЃЌЬхЛ§КЭЙІКФЖМКмДѓЃЌМлИёвВБШНЯЙѓЁЃЫцзХЮЂЕчзгММЪѕКЭМЦЫуЛњММЪѕЕФЗЂеЙЃЌвдDSPЮЂДІРэЦїМА DSPШэгВМўПЊЗЂЯЕЭГ(Р§ШчМЏГЩПЊЗЂЛЗОГCCS)МАХфЬзВњЦЗЮЊФкШнвбаЮГЩСЫХгДѓВЂМЋОпЧАЭОЕФИпаТММЪѕВњвЕЃЌЖјПЩБрГЬТпМЦїМўЁЂSOPCЕШаТММЪѕЕФгІгУбИЫйЩјЭИЕНЕчзгЁЂаХЯЂЁЂЭЈаХЕШСьгђЁЃетРяЗжБ№НшжњDSPаОЦЌдЫЫуЫйЖШИпЃЌЙІКФЕЭЃЌЪЕЪБЗжЮіЕФгХЪЦвдМАSOPCММЪѕСщЛюЕФПЩХфжУадЁЂНЯИпЕФПЩППадЁЂгВМўЩ§МЖШнвзЕШгХЕуЩшМЦСЫе§ЯваХКХЗЂЩњЦїЃЌВЂЖдИїздЩшМЦЙ§ГЬМАгХШБЕуНјааСЫЖдБШЁЃ 1 ЛљгкDSPЩшМЦе§ЯваХКХЗЂЩњЦї

1ЃЎ1 е§ЯвВЈВњЩњдРэ

вЛАуЧщПіЃЌВњЩње§ЯвВЈЕФЗНЗЈгаСНжжЃКВщБэЗЈКЭЬЉРеМЖЪ§еЙПЊЗЈЁЃВщБэЗЈЪЧЪЙгУБШНЯЦеБщЕФЗНЗЈЃЌгХЕуЪЧДІРэЫйЖШПьЃЌЕїЦЕЕїЯрШнвзЃЌОЋЖШИпЃЌЕЋашвЊЕФДцДЂЦїШнСПКмДѓЁЃЬЉРеМЖЪ§еЙПЊЗЈашвЊЕФДцДЂЕЅдЊЩйЃЌОпгаЮШЖЈадКУЃЌЫуЗЈМђЕЅЃЌвзгкБрГЬЕШгХЕуЃЌЖјЧвеЙПЊЕФМЖЪ§дНЖрЃЌЪЇецЖШОЭдНаЁЁЃБОЮФВЩгУСЫЬЉРеМЖЪ§еЙПЊЗЈЁЃвЛИіНЧЖШЮЊІШЕФе§ЯвКЭгрЯвКЏЪ§ЃЌПЩвдеЙПЊГЩЬЉРеМЖЪ§ЃЌШЁЦфЧА5ЯюНјааНќЫЦЕУЃК

ЪНжаЃКxЮЊІШЕФЛЁЖШжЕЃЌx=2ІаfЃЏfs(fsЪЧВЩбљЦЕТЪЃЛfЪЧЫљвЊЗЂЩњЕФаХКХЦЕТЪ)ЁЃ 1ЃЎ2 гВМўЩшМЦ

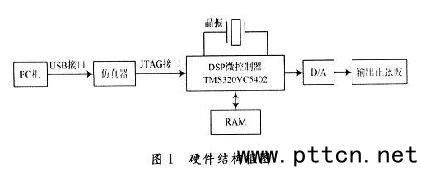

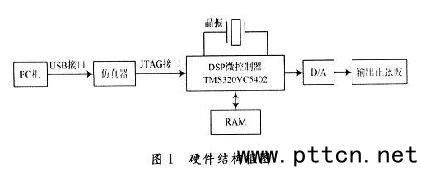

ЯЕЭГгВМўжївЊгЩЮЂЛњЁЂDSPаОЦЌЁЂЪ§ЃЏФЃзЊЛЛФЃПщзщГЩЁЃЦфжаЃЌDSPаОЦЌВЩгУЕФЪЧTIЙЋЫОадМлБШСМКУЕФTMS320VC5402ЁЃЫќгавЛзщГЬађзмЯпКЭШ§зщЪ§ОнзмЯпЁЂИпЖШВЂааадЕФЫуЪѕТпМЕЅдЊALUЁЂзЈгУгВМўТпМЦЌФкДцДЂЦїЁЂдіЧПаЭHPIПкКЭИпДя100 MHzЕФCPUЦЕТЪЁЃЫќПЩвддквЛИіжмЦкРяЭъГЩСНИіЖСКЭвЛИіаДВйзїЃЌВЂЧвОпгазЈУХЕФгВМўГЫЗЈЦїЃЌЙуЗКВЩгУСїЫЎЯпВйзїЃЌЬсЙЉЬиЪтЕФDSPжИСюЃЌПЩвдгУРДПьЫйЕиЪЕЯжИїжжЪ§зжаХКХДІРэЫуЗЈЁЃDЃЏAВЩгУСЫвЛжжЫЋМЋаЭ8ЮЛЁЂЕЭЙІКФЪ§ЃЏФЃзЊЛЛЦїDAC08ЃЌЪЕЯжСЫИпЫйЭЌВНЪ§ЃЏФЃзЊЛЛЁЃгВМўНсЙЙПђЭМШчЭМ1ЫљЪОЁЃ

1ЃЎ3 ШэМўЩшМЦ

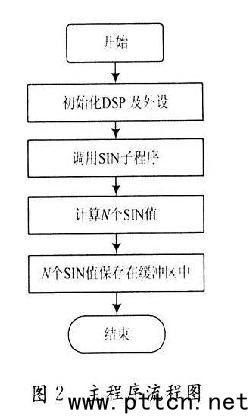

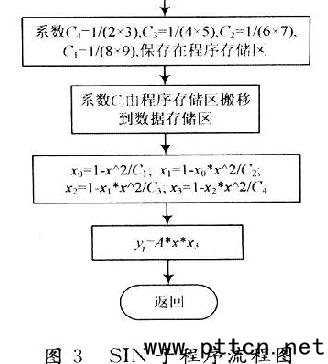

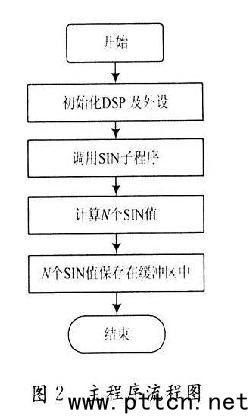

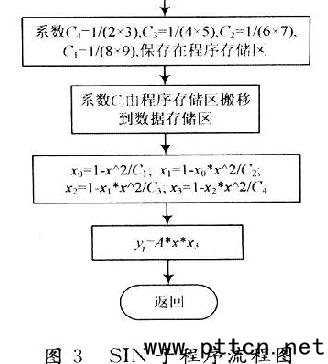

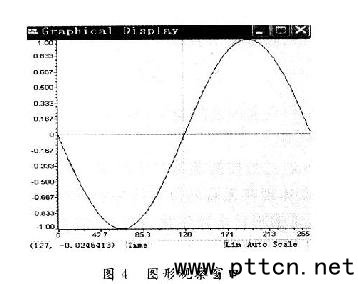

ШэМўЩшМЦЪЧЛљгкCCSПЊЗЂЛЗОГЕФЁЃCCSЪЧTIЙЋЫОЭЦГіЕФЮЊПЊЗЂTMS320ЯЕСаDSPШэМўЕФМЏГЩПЊЗЂЛЗОГЃЌЪЧФПЧАЪЙгУзюЮЊЙуЗКЕФDSPПЊЗЂШэМўжЎвЛЁЃЫќЬсЙЉСЫЛЗОГХфжУЁЂдДЮФМўБрвыЁЂБрвыСЌНгЁЂГЬађЕїЪдЁЂИњзйЗжЮіЕШЛЗНкЃЌВЂАбШэЁЂгВМўПЊЗЂЙЄОпМЏГЩдквЛЦ№ЃЌЪЙГЬађЕФБраДЁЂЛуБрЁЂГЬађЕФШэгВМўЗТецКЭЕїЪдЕШПЊЗЂЙЄзїдкЭГвЛЕФЛЗОГжаНјааЃЌДгЖјМгЫйШэМўПЊЗЂНјГЬЁЃБОЮФВЩгУСЫгыгВМўПЊЗЂАхЯрНсКЯЕФдкЯпБрГЬФЃЪНЃЌЭЈЙ§CCSШэМўЦНЬЈЩЯгІгУCгябдМАC54XЛуБргябдРДЪЕЯже§ЯваХКХЗЂЩњзАжУЁЃ ШэМўЩшМЦЕФЫМЯыЪЧЃКе§ЯвВЈЕФВЈаЮПЩвдПДзїгЩЮоЪ§ЕузщГЩЃЌетаЉЕугыxжсЕФУПвЛИіНЧЖШжЕЯрЖдгІЃЌПЩвдРћгУDSPДІРэЦїДІРэДѓСПжиИДМЦЫуЕФгХЪЦРДМЦЫуxжсУПвЛЕуЖдгІЕФyЕФжЕ(дкxжсШЁNИіЕуНјааБЦНќ)ЁЃећИіЯЕЭГШэМўгЩжїГЬађКЭЛљгкЬЉРееЙПЊЗЈЕФSINзгГЬађзщГЩЃЌЯргІЕФШэМўСїГЬЭМШчЭМ2КЭЭМ3ЫљЪОЁЃ

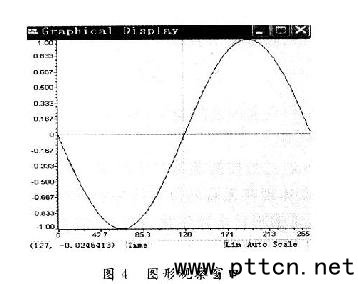

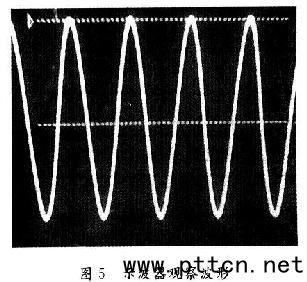

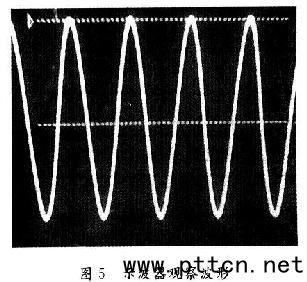

ГЬађжаЃЌNжЕЮЊВњЩње§ЯваХКХвЛИіжмЦкЕФЕуЪ§ЃЌВњЩњЕФе§ЯваХКХЦЕТЪгыNЪ§жЕДѓаЁМАDЃЏAзЊЛЛЦЕТЪfDAгаЙиЃЌВњЩње§ЯвВЈаХКХЦЕТЪfЕФМЦЫуЙЋЪНЮЊЃК f=fDA/N вђДЫЃЌбЁдёУПИіе§ЯвжмЦкжаЕФбљЕуЪ§ЃЌИФБфУПИіВЩбљЕужЎМфЕФбгГйЃЌМДЭЈЙ§ЕїНкNжЕВњЩњВЛЭЌЦЕТЪЕФВЈаЮЃЌЭЌЪБвВПЩвдРћгУШэМўИФБфЪфГіЕФРыЩЂВЈаЮжЕГЫвдЯргІЕФЫѕЗХвђзгAЃЌДгЖјЕїНкВЈаЮЕФЗљЖШЁЃНЋГЬађзАдиЕНDSPФПБъаОЦЌжаЃЌВЈаЮЪЕЯжНсЙћПЩвддкCCSЭМаЮЯдЪОНчУцжБЙлЕиБэЪОГіРД(МћЭМ4)ЛђепгУЪОВЈЦїЙлВьЪфГіНсЙћШчЭМ5ЫљЪОЁЃ

ЪфГіНсЙћЯдЪОЃЌдкCCSЭМаЮЙлВьДАПкЕУЕНСЫЦЕТЪЮШЖЈЃЌаХКХИЩШХаЁЃЌВЈаЮЪЇецЖШНЯаЁЕФе§ЯваХКХЃЛРћгУЪОВЈЦївВПЩЙлВьЕНВЈаЮНЯКУЃЌЮШЖЈЕФе§ЯваХКХЁЃ ЕчТЗФЃаЭЩшМЦЭъГЩКѓЃЌПЩвдРћгУSimulinkЛЗОГЕФЧПДѓЕФЭМаЮЛЏЗТецбщжЄЙІФмЃЌжБНгНјааЫуЗЈМЖФЃаЭЗТецбщжЄЃЌНсЙћШчЭМ8ЫљЪОЁЃгЩгкдкMatlabЕФ SimulinkжаЃЌФЃаЭЗТецЪєгкЯЕЭГбщжЄаджЪЕФЗТецЃЌВЂВЛЪЧRTLМЖЗТецЃЌгыФПБъЦїМўКЭгВМўЯЕЭГУЛгаЙиЯЕЁЃвђДЫВЩгУModelsimЖдЩшМЦЕчТЗНјааЙІФмЗТецЁЃModelsimЪЧMentorЙЋЫОНмГіЕФHDLЗТецЙЄОпЃЌвдЦфЧПДѓЕФЪ§зжКЭФЃФтЗТецЙІФмЖјЙуЗКгІгУЃЌЧвЗТецНсЙћжБЙлЁЂвзЖЎЃЌШчЭМ9ЫљЪОЁЃ 2 ЛљгкSOPCММЪѕЩшМЦе§ЯваХКХЗЂЩњЦї

ОЁЙмDSPДІРэЦї(ШчTIЕФTMS320ЯЕСа)дкЙ§ШЅКмГЄвЛЖЮЪБМфМИКѕЪЧDSPгІгУЯЕЭГКЫаФЦїМўЕФЮЉвЛбЁдёЁЃЕЋгЩгкЦфздЩэЕФОжЯоадЃЌР§ШчВЛСщЛюЕФгВМўНсЙЙЃЌЪЙЕУЦфКмФбТњзуЕБНёбИЫйЗЂеЙЕФDSPгІгУЪаГЁЁЃЯжДњДѓШнСПЁЂИпЫйЖШЁЂФкЧЖгаИїжжDSPФЃПщЕФFPGAКЭЯргІЕФSOPCММЪѕГіЯжЃЌЪЙЕУЪ§зжаХКХДІРэЕФЪЕЯжИќМгШнвзЁЃ 2ЃЎ1 DDFSдРэ

жБНгЪ§зжЦЕТЪКЯГЩ(DDFS)ЕчТЗгЩЯЕЭГЪБжгЁЂЯрЮЛРлМгЦїЁЂЦЕТЪРлМгЦїЁЂВЈаЮВщевБэЁЂDЃЏAзЊЛЛЦїКЭаХКХЕїРэЕчТЗЙЙГЩЁЃDDFSЕФЙЄзїдРэЪЧдкУПИіЪБжгжмЦкЃЌгУЦЕТЪРлМгЦївдЪфШыЦЕТЪзжFWЮЊВННјНјаазддіРлМгЃЌРлМгНсЙћЕФИпЮЛЫЭЯрЮЛРлМгЦїЃЌВЂгыЪфШыЕФЯрЮЛзжPWНјааРлМгЃЌЯрЮЛРлМгЕФЪфГізїЮЊВЈаЮВщевБэЕФЕижЗЃЌДгВщевБэжаЖСГіЯргІЕФЪ§ОнЫЭИјDЃЏAзЊЛЛЦїЃЌзюКѓОЙ§ЕЭЭЈТЫВЈЦїЁЂКѓМЖЗХДѓЕШаХКХЕїРэЕчТЗЃЌвдаЮГЩФЃФтСПВЈаЮЪфГіЁЃЭМ6ИјГіЯЕЭГНсЙЙПђЭМЁЃ

(жаЙњМЏШКЭЈаХЭј | д№ШЮБрМЃКГТЯўСС) |