用FPGA实现TETRA数字集群通信系统语音信道编码中的交织器

时间:2017-06-16 来源:中国集群通信网 作者:网络 点击:

次

主页(http://www.pttcn.net):用FPGA实现TETRA数字集群通信系统语音信道编码中的交织器

交织技术能很好地纠正信息传输过程中出现的突发性错误。在数字信息传输系统中得到了广泛应用。本文将在讨论信息产业部重点支持发展的TETRA数字集群通信系统语音信道编码结构和流程的基础上,重点研究交织技术在其语音信道编码中的应用及用FPGA实现该交织器的方法。

1 语音信道编码流程

TETRA数字集群系统中,语音信号数字化处理再经过ACELP算法[1]编码后得到低速率的语音数据流,该语音数据流分为三类,分别为:每帧(30 ms)0类为51比特、1类为56比特、2类为30比特。

在这三类中,2类是最关键的。2类比特用CRC码和卷积码来保护,1类比特只用卷积码来保护,而0类比特是没有保护的。根据TETRA数字集群标准,将2个连续的30 ms(精确为29.97 ms)语音信息组合并。第一步把0类、1类和2类比特组合成一个群,产生一个代表60 ms话音的274比特的单组。2类比特通过一个CRC码产生8比特校验码,并加到2类子组的尾部。卷积码既适用于1类比特,又适用于2类比特。4比特的尾部加到重新设置的编码器状态上。这里采用一种经济的收缩码以3/2速率用于1类比特,以18/8速率用于2类比特、奇偶校验比特和尾部。

然后,所合成的330比特与无保护的0类比特重新合并,形成一个432比特组。最后对形成的432比特组进行时隙内的比特交织[2],形成新的数据比特流,最后将该数据比特流与系统其他信息比特流复用,经过调制后送入无线信道。

在信道编码中采用交织技术,将连续的突发错误分散,使其转换为随机错误,从而提高整个通信系统的可靠性。下面将主要研究语音信道编码中如何使用交织技术。

2 交织器工作原理

数字通信中常用的交织器按交织对象分可分为字节交织和比特交织。这里以比特交织为例介绍一下交织器的工作原理。

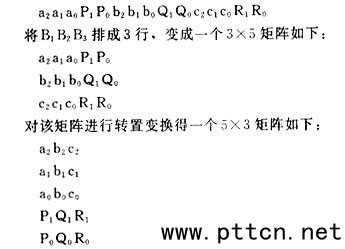

假设有3个要传输的(5,3)码块B1,B2,B3为:

不采用交织技术在信道上传输的数据比特流为:

变换后即交织处理后在信道上传输的数据比特流为:

假设不采用交织技术接收端收到数据为(“×”表示传输过程中出错的数据):a2a1a0P1P0b2b1×××c2c1c0 R1R0。因为传输的是(5,3)码块,这样每个码块中出现一位错误可以纠正,故对码块b2 b1×××连续突发出现的三位错误就无法进行纠正了。如果采用交织编码后再传输数据,接收端收到数据应为:a2b2c2a1 b1c1 a0×××Q1R1 P0 Q0 R0。接收端再对数据进行序列变换得:a2 a1a0×P0b2 b1×Q1Q0c2c1×R1 R0。这样连续突发出现的三位错误就分散到3个码块中,均可得到纠正。

一般来说,如果有r个(n,k)码,排成r×n矩阵,按列交织后存储或传送,读出或接收时恢复原来的排列,若(n,k)码能纠t个错误,那么交织后就可纠rt个错误[3]。对纠正信道传输过程中出现的突发错误效果明显。TETRA语音信道编码中使用这种比特交织器。

3 用FPGA实现交织器的方法

TETRA数字集群系统语音信道编码对语音比特流进行交织编码时,以CRC和FEC编码后一个时隙内432比特的语音数据流为处理单位,分成18行,每行24比特,进行比特交织编码。

根据Altera公司FLEX系列器件的内部结构特点,可以利用EAB资源,用存储器实现TETRA数字集群语音信道编码中的交织器。这种方法实现起来比较简单,可以用现有的逻辑器件LPM-RAM-DP来实现。

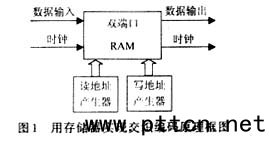

考虑到语音实时传输过程延时要尽可能小,在此选用双口RAM,以保证能对存储器的缓冲区同时读写,减小延时。因为24×18=432<1 024,故容量用1kB即可,图1为实现该交织器的原理框图。交织器实际工作时,先将一个时隙内(60 ms)的432比特语音数据流按地址从0~431全部写入左RAM,432比特的数据全部送达左RAM后,用分频器产生控制信号使左RAM由写状态转换为读状态,可以从中读出交织处理后的数据。同时右RAM状态变为写,下一时隙的432比特数据写入右RAM,432比特的数据全部送达右RAM后,用分频器产生控制信号使右RAM由写状态转换为读状态,同时左RAM变成写状态,依次反复循环完成交织编码。

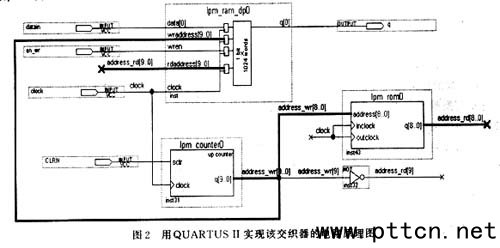

这种实现交织编码的方法是将输入的数据直接存入存储器,存储的顺序由地址确定。然后再将这些数据按照一定的顺序读出来,顺序也是由地址确定。因此做一个合适的地址产生器便能满足交织编码的要求,使用Altara的开发工具QUARTUS可以实现对该交织器的仿真。图2为使用QUARTUSII实现该交织器的电路原理图。

这是基于FLEX10K的EPF10K30EFC256-1器件实现的交织器,在QUARTUSII编辑器中,在lpmrom0存储器中存储满足交织编码的数据地址变换程序,仿真后编码延迟远小于60 ms(一个时隙),满足TETRA数字集群系统语音信道编码中交织编码的要求。

4 结 语

随着通信技术的发展,我国现有的模拟集群通信系统必将被数字集群通信系统所代替。本文针对信息产业部重点支持发展的TETRA数字集群通信系统,详细介绍了该系统语音信道编码结构和流程,分析了信道编码中采用的交织技术,针对语音通信的特点,详细介绍了用FPGA实现TETRA数字集群通信系统语音信道编码中的交织器的方法。为进一步研究TERTA数字集群通信系统和信道编码打下了良好的基础。

参考文献

[1]傅寅飞,刘亚康,朱学勇.全数字集群系统(TETRA)声码器的仿真与实现[J].移动通

[2]苏闽,张乃通,谭学治,等.交织编码在TETRA数字集群系统语音业务信道中的性能研究[J].移动通信,2002,(5):39-42.

[3]林福宗.多媒体技术基础[M].北京:清华大学出版社,2000.

(编辑:chiying)

(中国集群通信网 | 责任编辑:李俊勇) |