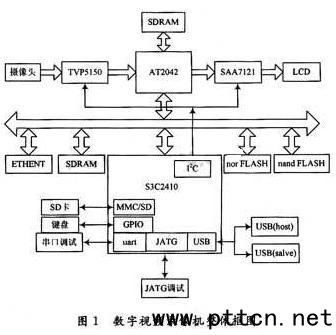

主页(http://www.pttcn.net):基于MPEG-4视频标准数字视频录像机的设计与实现 1 数字视频录像机的硬件设计 (1)实现对视频数据的MPEG-4标准的编解码; (2)编解码像素为720X576像素点,实现25 f/s; (3)实现JPEG编码和解码; (4)实现USB/SD卡储存。 1.1 基于S3C2410与AT2042的数字视频录像机整体设计

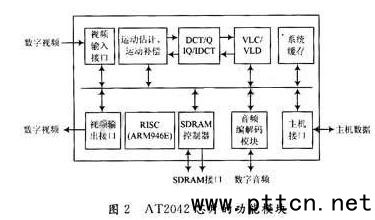

韩国Pentamicro公司生产的AT2042芯片的功能模块如图2所示,AT2042是一个内置微控制器ARM946E的2通道音视频编解码 (A/VCODEC)芯片,主要完成对视频和语音数据的编码和解码,支持多种音视频编解码标准,可直接与IBM,Motorola,ARM,XscaIe 和Axis等多种CPU接口,无需其他附加电路。

1.2 视频编解码电路设计

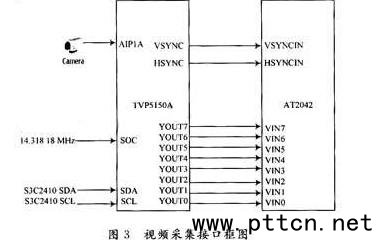

摄像头采集输出信号为NTSC,PAL或SECAM制式的电视信号,必须经过视频解码处理才能转化成适合AT2042进行编码的数字信号。 TVP5150是TI公司生产的一款电视信号解码专用芯片,它对输入的模拟信号进行A/D转化,通过设置相应的寄存器可以使输出信号满足RGB格式或 YUV422格式。由于在本系统中AT2042视频接口满足ITU.RBT656标准,故TVP5150输出配置为8位YUV422格式。 视频输出如图4所示。

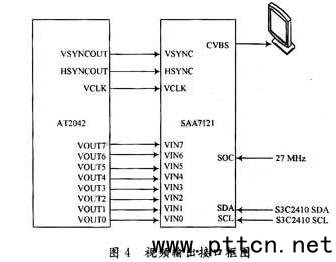

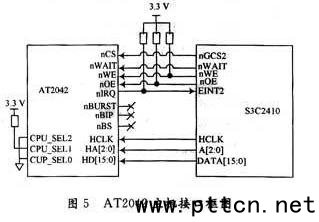

现在的数字电视视频接口还没有实现统一的工业标准,故在视频输出端设计时,仍使用现在比较流行的A/V接口或S-video接口。由于上述2种接口传输的为模拟电视信号,故在AT2042的视频输出端口需要增加一级处理,即将数字信号转化为模拟电视信号。在后端设计中选用SAA7121,它是一款专用的电视信号编码芯片,可以将输入的数字信号经过内部的D/A转化为适于传输的模拟电视信号,通过配置相应的寄存器可以输出满足S-video接口或复用接口的信号。 1.3 AT2042的主机接口 图5为S3C2410与AT2042接口框图。

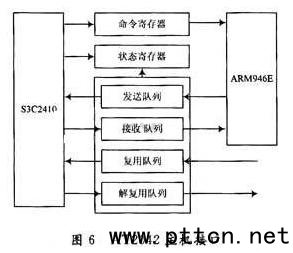

AT2042的CPU_SEL[2:0]是主控CPU选择引脚,经配置这几个引脚的高低电平,使AT2042可选择主控CPU,CPU_SEL[2:0]为010选择ARM结构芯片; nCS,nWAIT等为总线控制信号线; HCLK是AT2042主机接口的工作时钟,一般要求工作在50 MHz,当S3C2410在复位后设置FCLK为200MHz,HCLK为100 MHz,PCLK为50 MHz。故将S3C2410的PCLK引脚与AT2042的HCLK引脚相连。 通过这种机制,S3C2410可以实现简单的访问AT2042。 AT2042与CPU的通信机制如图6所示,CPU对AT2042的控制和访问主要通过AT2042的2个寄存器(status register和command register)和4个FIFO(Tx FIFO,Rx FIFO,Multiplex FIFO和De-Multiplex FIFO)完成。

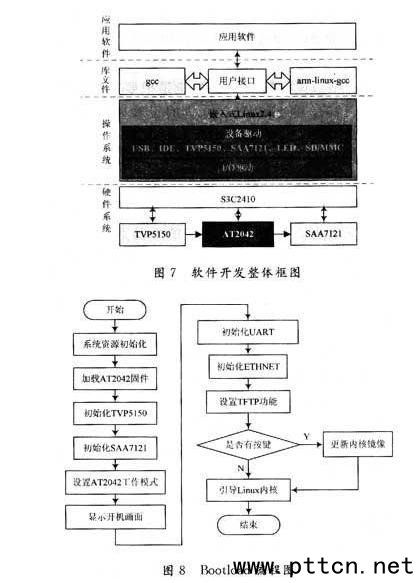

2 数字视频录像机的软件实现 数字视频录像机软件开发的整体架构如图7所示。

|