主页(http://www.pttcn.net):FED矩阵扫描功率放大电路的研究

场致发射显示器(Field Emission Display,FED)是一种新型的平板显示器件,被认为是最有可能与等离子体(PDP)和液晶显示器(LCD)相竞争的平板显示器,它具有反应速度快,重量轻,功耗小,视角大,颜色鲜艳等优点,满足消费者对显示品质的要求,具有可观的市场前景。FED产生图像的原理与阴极射线管(CRT)相同,均为电子轰击荧光粉发光,但采用的是矩阵寻址的方式。FED驱动电路是FED研发的重中之重,福州大学在国家科技部和地方相关科技部门以及国内多家大型企业的关心支持下,已研制出25英寸具有自主知识产权的彩色大屏幕低逸出功印刷式场致发射显示器。根据FED矩阵寻址的特点,设计出了相应的矩阵扫描功率放大电路,包括分立和集成驱动以及结合分立和集成优点的混合型驱动电路。这些电路已经应用在25英寸QVGA,VGA的FED中,并将在34英寸FED驱动电路中得到进一步的应用。 1 FED矩阵扫描功率放大电路的特点

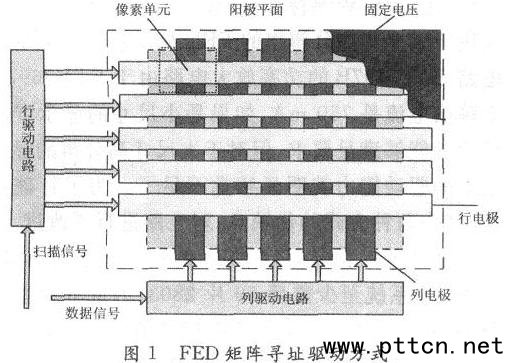

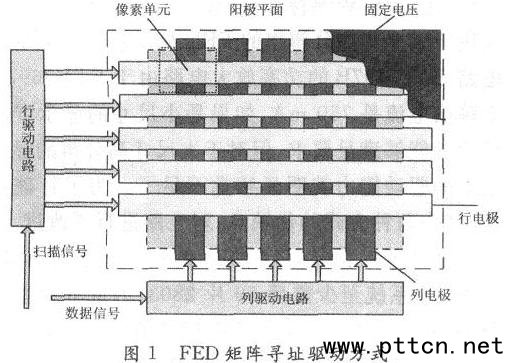

如图1所示,FED和大多数平板显示器一样,也是采用行列矩阵选址驱动工作方式,阳极加固定电压,栅极作为行电极,阴极作为列电极,每个行列电极交叉点就构成了一个像素单元。阳极电压由荧光粉所需的工作电压决定,行电极是逐行或者隔行加上扫描电压的,列电极加上视频图像信号,行列电压差产生场电子发射,电子在阳极电压的加速下轰击荧光粉发光。行电极的功能就是寻址扫描,并在行扫描期间,汇集所有列的电流,提供系统所需功耗。如VGA系统,设计的目标是列驱动电压脉冲幅度为100 V,电流脉冲幅度最大为6 mA,电子发射时行收集的电流最大为3.84 A,对于更高分辨率的系统来说这个数值还会更高,这对栅极高压功率放大电路提出了大电流和相对较大电压(100~200 V)的要求。这就要求在选择高压驱动晶体管或者MOS管的时候要充分照顾到电压和电流的要求,并且稳定性要相当好。对于集成电路来说要满足这个要求会更加的困难,因为集成电路的制作工艺限制,在市场上现在还找不到为FED驱动电流研制的专用芯片,借鉴PDP电路设计法,设计了一种基于PDP专用芯片 STV7696B的行集成系统。

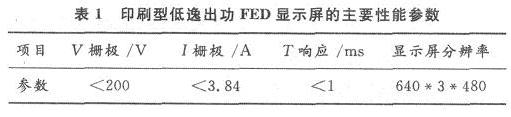

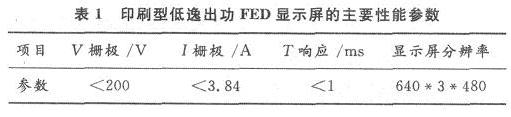

实测FED阴极的逸出功典型值约为2 eV,实验测试的FED阴极的发射电流典型值约为3 mA/像素,最小阴极发射面积为O.4 mm×O.4 mm。表1是印刷型FED显示器的主要性能参数。

2 分立式矩阵扫描功率放大电路

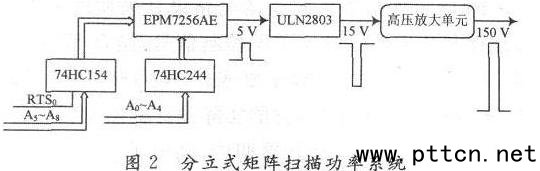

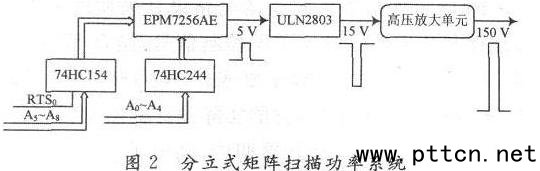

基于分立式的矩阵扫描功率系统是CPLD可编程器件完成对主板提供的行信号进行译码,然后再经过高压MOS管的功率放大,完成整个系统。其系统框图如图2所示。

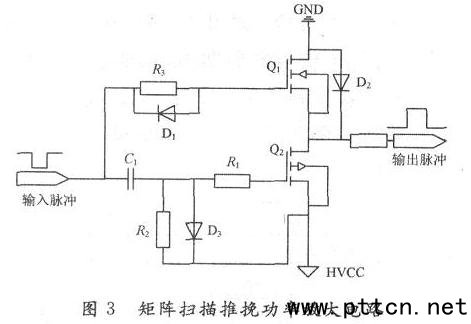

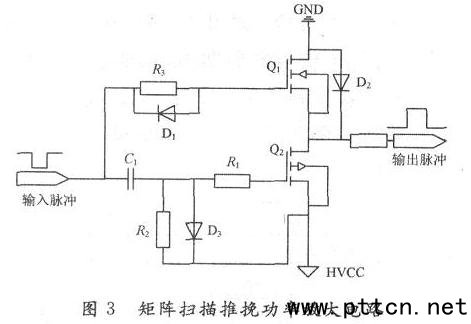

高压功率放大部分不仅要对前级的低压扫描脉冲进一步拉高,同时还要提供电流负荷能力,这样才能对列功率系统的灰度显示提供足够的电流。一般的晶体管和MOS管提供电流只有数百毫安,这对于系统来讲可能会有提供功率不足的现象,所以功率型MOS管是该设计的最佳选择。 如图3所示,采用的是由功率型MOS管组成的推挽电路,低压扫描脉冲进入到高压驱动单元进行放大。电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。图3中MOS管Q1,Q2的参数相同,以推挽方式存在于电路中。当脉冲为高电平时,Q1管导通,Q2管截止,电路输出低电平;当脉冲为低电平时,Q1管截止,Q2管导通,电路输出高电平。通过两只MOS管的交互导通,从而减低了功耗,提高了每个管的承受能力,适合于FED驱动大电流的要求。由电阻R2和二极管D3组成的并联钳位电路,目的是使MOS的导通速度加快。

3 集成矩阵扫描功率放大电路

3.1 STV7697B简介

STV7697B是ST公司生产的一种专用于PDP的扫描驱动芯片,拥有一个频率高达8 MHz的64位的级联移位寄存器,可以实现64路高压大电流输出。通过级联,可以实现任意的垂直像素。低压部分逻辑控制采用5 V的电压,高压部分最大供电电压为170 V,所有的输入均与CMOS兼容。STV7697B同时还具有以下特点:

(1)峰值输出电流一200/750 mA;

(2)最大源极输出电流1 A;

(3)消隐信号控制;

(4)互补的输出控制;

(5)100脚的TQFP封装。 3.2 STV7697B驱动方案

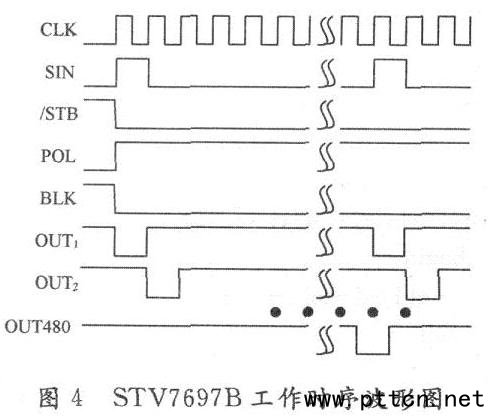

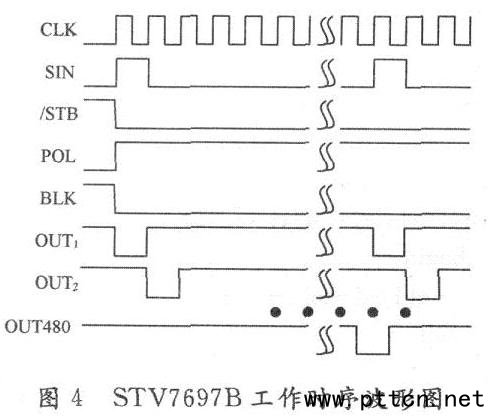

图4是芯片的工作时序波形图,工作时SIN脚接收从控制板发出的扫描信号,极性传输方向选择控制端F/R选择传输方向,信号在行同步时钟CLK的上升沿变化瞬间在移位寄存器中移位前进,在STB控制下移位寄存器的数据就放到锁存器中,当BLK允许输出时,信号经过内部功率放大器增益输出相应的高压信号。

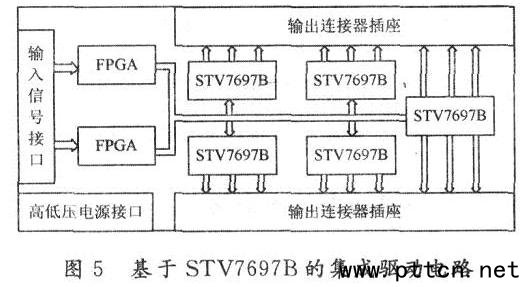

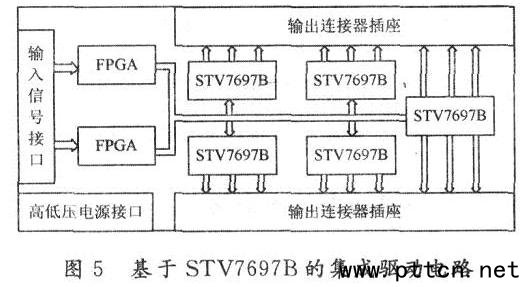

FED矩阵扫描集成驱动电路设计采用的是FPGA芯片控制产生行驱动所需的控制信号,结合STV7697B芯片的内部结构以及时序要求。STV7697B 可级联使用,实现矩阵扫描输出,它的实际设计框图如图5所示。行电路工作时,每一个行周期内,高电平有效的SIN信号先从第一片STV7697B的SIN 端输入,从芯片的SOUT端输出,再与后一芯片的SIN端级联。这样,在行扫描脉冲CLK信号的周期内,扫描数据电平从第一个输出端依次移位到最后一个输出端,各信号经过内部功率放大器增益输出相应行的扫描脉冲,加载到FED显示屏行电极上。

3.3 STV7697B软件设计

根据FED系统的要求,如VGA系统,扫描一行的时间是64 μs,从主板传输过来的信号是8位地址信号和奇偶场鉴别信号,其8位地址信号是通过分频得到的,周期最短的信号a[O]周期64μs,可以采用上升沿触发的方式,在奇偶场信号RTSO为低的时候,当a[0]上升沿到来时,令SIN=1,CLK=a[0],清场信号CLR为低,同时计数器n开始计数,a[0]每到来一次上升沿,n就加1,当n>1时,SIN=0;而当RTSO为高时,清场信号为高,同时另外一场开始工作。其中信号/STB,POL,BLK和F/R均由FPGA设定值输出。在一帧图像的时间内,扫描时钟从第一行扫描到第480行,当下一帧到来时,重复前面的过程。

(中国集群通信网 | 责任编辑:陈晓亮) |